Its use results in faster development, cleaner testbenches, and a modern software-oriented approach to validating FPGA and ASIC designs without replacing your existing simulator.

Verification has always been one of the most resource-intensive phases of digital design. Whether building FPGA-based embedded controllers or high-complexity ASICs, engineers spend substantial time validating RTL functionality before committing to hardware or silicon. Traditionally, this validation relies on SystemVerilog or VHDL testbenchespowerful but often verbose, rigid, and demanding to maintain as design scale.

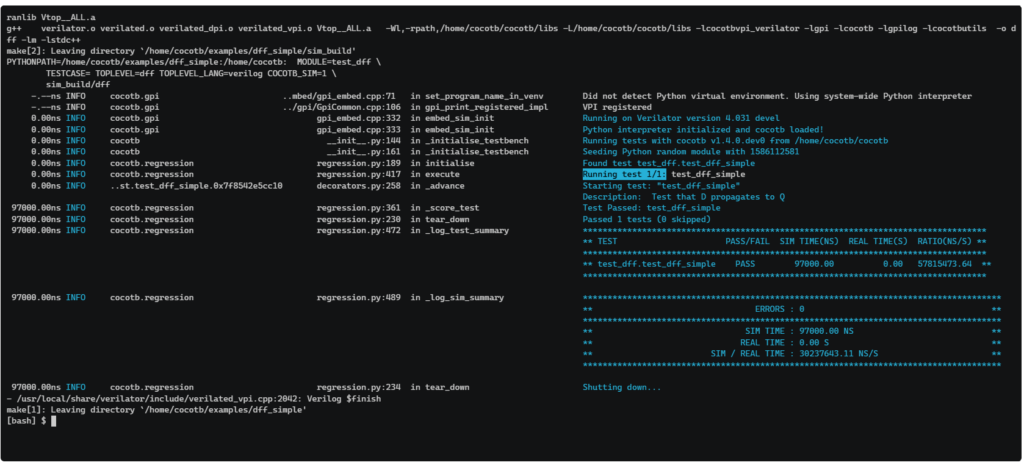

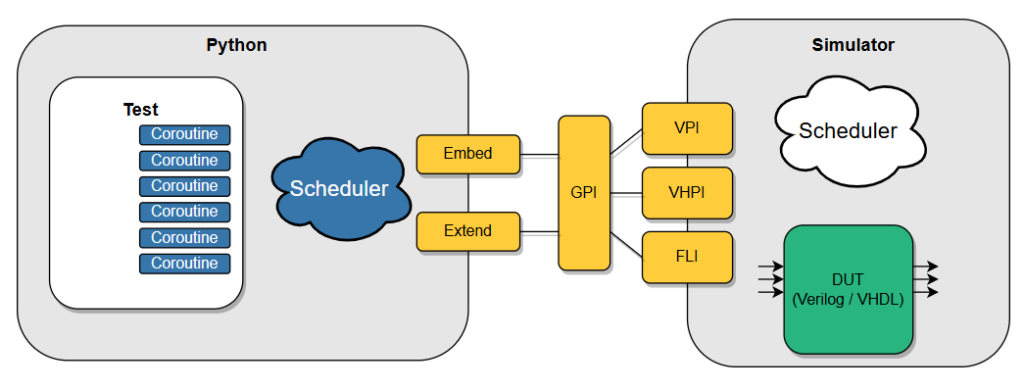

Cocotb (Coroutine-based Cosimulation TestBench) introduces a fundamentally different approach. Instead of writing testbenches in HDL, engineers write verification logic in Python. The hardware design still runs inside a conventional HDL simulator, but stimulus generation, monitoring, protocol checks, logging, and automation are handled using Python scripts.

This shift may sound simple, but its impact on productivity, maintainability, and workflow integration is significant. Cocotb effectively bridges hardware simulation with modern software engineering practices, enabling teams to verify digital systems faster and more efficiently.

What Cocotb Actually Is

Cocotb is an open-source verification framework that connects Python-based test code to HDL simulators via a cosimulation interface. It does not replace your simulator or RTL toolchain. Instead, it layers Python-driven verification on top of them.Here’s how it works:

- Your RTL (Verilog, SystemVerilog, or VHDL) runs in a simulator.

- Cocotb attaches to the simulator through a standard interface.

- Python coroutines drive signals, wait for events, check outputs, and log results.

- Test execution and reporting are managed through a built-in Python-based runner.

The RTL continues behaving exactly as it would in a traditional environment. The difference lies in how you write the testbench logic.This architecture makes Cocotb simulator-agnostic and flexible. It integrates with open-source simulators such as:

- Verilator

- GHDL

- Icarus Verilog

It also works with commercial tools including:

- Questa

- VCS

- Xcelium

- Riviera-PRO

This broad compatibility ensures that adopting Cocotb does not require replacing existing EDA investments.For design engineers, verification pain typically shows up in three areas: code complexity, test maintenance, and automation integration.The tool directly addresses all three.

1. Reduces Testbench Complexity:HDL-based testbenches can become verbose quickly, especially when modeling complex protocols or asynchronous interactions. Python, by contrast, offers concise syntax and rich abstraction capabilities.Instead of writing dozens of lines for simple operations, engineers can express intent clearly and compactly. Python’s readability also improves collaboration between hardware and software teams.Many engineers report that test development time decreases significantly when switching to Python-based verification.

2. Natural Handling of Concurrency:Digital hardware is inherently parallel. Cocotb leverages Python coroutines to model this concurrency naturally.Using async and await constructs, engineers can:

- Wait for clock edges

- Trigger on signal changes

- Run multiple stimulus threads simultaneously

- Coordinate complex timing relationships

This coroutine-driven model often feels more intuitive than HDL-based process blocks, especially for engineers familiar with modern software programming.

3. Access to the Python Ecosystem:One of Cocotb’s biggest strengths is immediate access to Python’s extensive ecosystem. Design engineers can easily integrate a wide range of tools into their workflow, including random stimulus generators, data parsing tools, logging frameworks, numerical libraries, automation scripts, and regression control utilities, enabling efficient development, testing, and validation processes.Complex data-driven testing such as reading protocol vectors from CSV files or generating patterned input sequences becomes straightforward.An FPGA engineer summarized the benefit clearly, “We used Python libraries to generate data-driven stimuli that would have taken days to implement in SystemVerilog.”

4. Seamless CI/CD Integration:Modern hardware teams increasingly rely on automation. Continuous integration pipelines now run nightly regressions, generate coverage reports, and enforce validation gates. It includes a built-in test runner that:

- Automatically discovers test functions

- Executes them without extensive configuration

- Produces JUnit-style XML output

This output integrates directly with CI platforms such as Jenkins or GitLab CI.One verification engineer commented:“The biggest gain wasn’t just Python it was how easily Cocotb plugged into our CI pipeline. Regression testing became painless.”For startups and FPGA teams building automated validation systems, this feature alone can justify adoption.

What’s New?

The 2.x release line represents a significant maturation of the framework, with a strong focus on long-term maintainability, API clarity, and improved tooling support. One of the key improvements is a cleaner and more structured API design. The interfaces have been refined for greater consistency and readability. Although some changes were introduced compared to earlier versions, the migration paths are well-structured and clearly documented. Developers upgrading from 1.x often report smoother transitions than expected, with one user noting that the anticipated friction moving to 2.0 was offset by API cleanup that ultimately simplified maintenance.

Coroutine scheduling has also been enhanced to provide better execution predictability and improved debugging clarity. This results in greater reliability, especially in complex and timing-sensitive verification environments. In addition, enhanced Python typing integration improves IDE auto-completion, enables stronger static analysis support, and makes navigation easier in large-scale test environments an important benefit for verification teams maintaining shared frameworks.

Logging and debugging capabilities have been further refined, with improved logging controls and formatting that deliver clearer test failure reports, better traceability, and more readable regression outputs. These enhancements help reduce debug cycles and increase productivity during failure analysis. Finally, ongoing updates ensure continued compatibility with evolving simulator versions across major platforms, including Linux, macOS, and Windows.

Performance Considerations

Because Cocotb operates through a cosimulation interface, some users observe that pure SystemVerilog UVM environments may execute faster in extremely large-scale ASIC regressions. However, many teams find that improvements in development speed, long-term maintainability, automation efficiency, and reduced debugging time more than compensate for any modest simulation overhead. In FPGA workflows and medium-scale ASIC environments, performance differences are often negligible when compared to the overall productivity gains.

One of Cocotb’s strongest advantages is its cost model. Cocotb is licensed under the BSD 3-Clause License, which means it is free for personal use, academic projects, and commercial deployment. There are no feature restrictions, subscription tiers, or enterprise paywalls there is no “premium edition,” and all framework capabilities are fully accessible.

As an open-source project, Cocotb benefits from active community discussions across forums and technical blogs. Common positive feedback includes sentiments such as, “Writing test logic in Python feels natural,” reflecting engineers’ appreciation for not having to maintain large HDL-based test infrastructures. Others note that it has transformed collaboration between hardware and software teams, allowing software developers to contribute directly to verification without deep HDL expertise. Teams also frequently mention that automation becomes straightforward, with CI integration reducing manual regression overhead and improving consistency. Finally, many highlight that complex stimulus generation is significantly easier thanks to Python’s powerful data-handling capabilities, which simplify advanced test scenarios.

That said, Cocotb requires an HDL simulator, and overall costs depend on the simulator selected. Open-source simulators such as Verilator, GHDL, and Icarus Verilog are free. Commercial simulators like Questa, VCS, Xcelium, and Riviera-PRO require paid licenses. Regardless of simulator choice, Cocotb itself remains free. For startups and research labs operating with limited budgets, this open-source model significantly lowers verification barriers.

Where it Fits Best

Cocotb is particularly well suited for FPGA development teams, startups building cost-sensitive products, research institutions, teams adopting CI-driven validation, and mixed hardware/software development groups. While it may not fully replace SystemVerilog UVM flows in extremely large ASIC verification programswhere standardized enterprise methodologies often dominatemany ASIC teams still leverage Cocotb effectively for subsystem validation, IP-level testing, or rapid prototyping.

Traditional verification methodologies treat testbenches primarily as extensions of HDL. Cocotb, in contrast, approaches verification as a software engineering discipline. This philosophical shift enables modular test architectures, greater code reuse, automated regression strategies, data-driven validation techniques, cleaner debugging workflows, and alignment with modern software development practices.

As one engineer described it:“Cocotb makes hardware testing feel like software testing. That fundamentally changes team productivity.”Verification remains one of the most complex and time-consuming aspects of digital design. Tools that increase productivity without compromising rigor are invaluable. Cocotb delivers Python-based verification, coroutine-driven concurrency, broad simulator compatibility, seamless CI/CD integration, clean and structured APIs in the 2.x series, zero licensing cost, and strong community support.

For design engineers seeking a modern, maintainable, and cost-effective verification methodology, Cocotb offers a compelling alternative to traditional HDL-based testbenches. It does not replace simulators it enhances them. It does not reduce hardware rigorit streamlines how validation is performed.In an industry where development cycles are accelerating and automation is no longer optional, that combination positions Cocotb as one of the most practical and forward-looking verification frameworks available today.